cpu topology

1.1. cpu拓扑

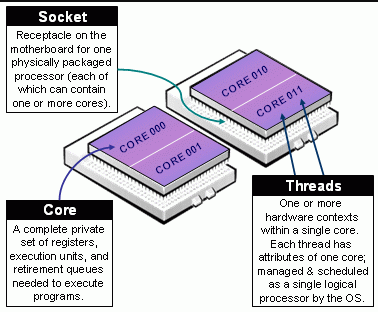

cluster(socket)->core->Threads(目前为止arm没有提出多线程的概念)

1.2 多核技术

基于制程,扩充性等考虑,芯片厂商会把多个core封装在一个chip上,称为socket。socket的概念在X86架构上使用尤其多,可以理解为插槽;

假设一个插槽上有两个core,那么我在主板上插2个插槽,就是4核系统,插上4个插槽就是8核;arm的话则是另外一个概念cluster,簇

在X86架构的PC上,唯一目的的话是提高CPU的处理性能(不在乎功耗),但在移动市场中(大多是arm),性能提高后,对应着就更多的power消耗;对于设备电源管理以及散热提出了更高的要求。与此同时电池并没有随着CPU的拓扑的进化而进化,于是HMP技术就被提出来了;

1.3HMP(Heterogeneous Multi-Processing)

big-little:

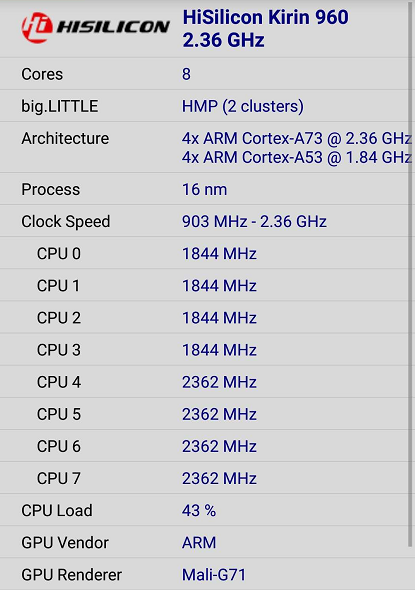

- 在一个chip中封装两类ARM Core,以kirin 960为例:一类为高性能Core,4核ARM A73,最高主频为2.4G,一类为低性能Core,4核ARM A53,最高主频为1.8G

DynamIQ:

- 在单一cluster内可有8个核心,且可由不同架构,时钟的核心组成,提升了运作效率与配置的弹性,如高通的845 4核ARM A75,最高为2.8,4核 ARM A55,最高为1.8G

DynamIQ较big-little好处:

- 单cluster可有8核心

- cluster可搭配不同架构的CPU

- 各cpu可有独立的运作时钟

- CPU各自开关休眠互不影响

- 依照效能需求弹性运用各核心

以龙舟比喻ARM的DynamIQ与先前的big.LITTLE技术,我们把龙舟当成cluster,船员当成core,那么big.LITTLE龙舟上只能有4个船员,而且每个船员身材需要一样(核心架构),划船的时候若多位船员一起划船时,每个人的出力均等(频率一致),不能有人慢划或者快划;

当使用DynamIQ时,每艘船(cluster)上可以有8位高低胖瘦不等(架构)的船员(core),换船频率可以不等,且船员可以依照指令睡觉(关闭),休息(休眠),或划船(运作);

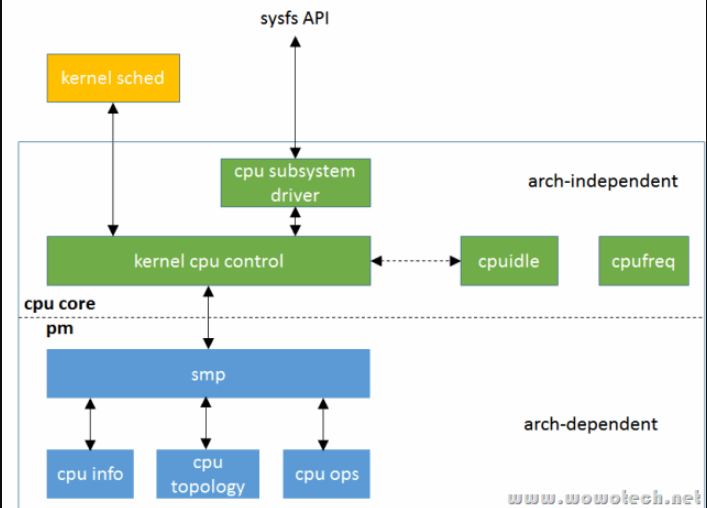

cpu内核代码框架

- 系统启动时,CPU core的初始化,信息获取

- 系统启动时,CPU core的启动(enable)

- 系统运行过程中,根据当前负荷,动态enable/disable 某些CPU core,以便在性能与功耗间平衡

- cpu core的hotplug支持,所谓的hotplug,是可以在系统运行的过程中,动态的增加或者减少CPU core(可以是物理上,也可以是逻辑上)

- 系统运行过程中CPU idle管理

- 系统运行过程中,根据当前负荷,动态的调整CPU core的电压和频率,以便在性能和功耗之间平衡

arch-depedent部分位于”arch\arm64\kernel”负责平台相关的控制操作,包括

1 | cpu 信息的获取(cpuinfo) |

arch-independent负责实现平台无关的抽象,包括

1 | cpu control模块,屏蔽底层平台相关实现细节,提供控制CPU(enable,disable等)的统一API,供系统启动,进程调度等模块调用 |

cpu的状态表示

- possible CPU: 就是在DTS中指定了的,物理存在的CPU core

1 | start_kernel->boot_cpu_init->smp_process_id用于获取cpu id |

- present cpu: 被kernel标识的,具备执行代码条件,后续可以在需要的时候(如hotplug的时候),启动该CPU

1 | start_kernel->rest_init->kernel_init->kernel_init_freeable |

- online CPU: 某个CPU是present的,不一定是boot,所谓CPU boot,就是让CPU执行(取指译码/执行)代码

- active CPU 只是为了方便调度器操作